ECS提供超全的振蕩器輸出類型指南

ECS提供超全的振蕩器輸出類型指南

隨著越來越多的生產(chǎn)廠家開始使用石英晶體振蕩器,關(guān)于相關(guān)的資料知識(shí)有更多的人在關(guān)注,振蕩器的主要參數(shù)選項(xiàng)有封裝尺寸,頻率,電源電壓,頻率公差,輸出方式,工作溫度等.只要選擇正確的參數(shù)就能找到合適的晶振,除此之外,部分廠家會(huì)指定某個(gè)品牌,ECS晶振是目前市場(chǎng)上比較受歡迎的一家,其頻率元件種類齊全,幾乎可以找到任何一款想要的晶體和振蕩器.同時(shí)ECS公司也會(huì)不定時(shí)的發(fā)布一些與晶振相關(guān)的文章,以下內(nèi)容就是他們家關(guān)于振蕩器輸出類型全面的知識(shí)資料.

關(guān)于振蕩器的最常見問題是:單端和差分輸出之間有什么區(qū)別,它們最適合什么應(yīng)用?

根據(jù)應(yīng)用和所需的操作頻率,有幾種輸出類型可供選擇.這里更詳細(xì)地介紹了一些不同的晶振輸出,以更好地理解每個(gè)輸出的好處和取舍.這應(yīng)該使您更好地了解哪種類型最適合您的應(yīng)用程序.

有兩種主要的輸出格式.

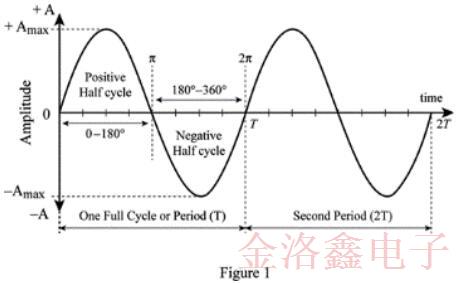

正弦波-如下圖所示,創(chuàng)建了一個(gè)連續(xù)的模擬正弦波,以頻率和幅度的速率掃描周期表示.

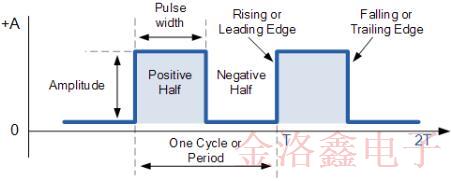

方波-如下圖所示,是振蕩器輸出的數(shù)字表示.它的信號(hào)以頻率和幅度的速率由90度周期表示.

我們將介紹的輸出是:

單端輸出:正弦波和削波正弦波

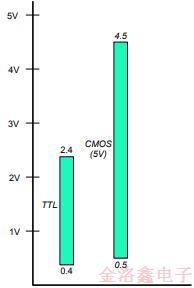

TTL(晶體管到晶體管邏輯)0.4~2.4V

CMOS(互補(bǔ)金屬氧化物半導(dǎo)體)0.5~4.5V

HCMOS(高速CMOS)0.5~4.5V

LVCMOS(低壓CMOS)0.5~4.5V

差分輸出:

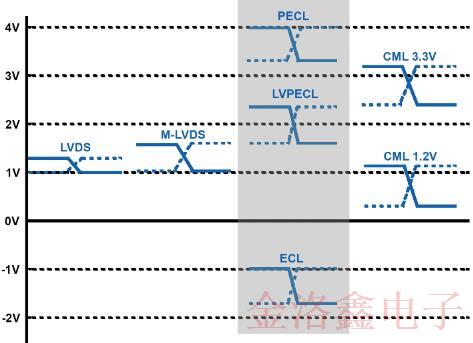

PECL(正發(fā)射極耦合邏輯)3.3~4.0V

LVPECL(低壓PECL)1.7~2.4V

CML(電流模式邏輯)0.4~1.2V和2.6~3.3V

LVDS(低壓差分信號(hào))1.0~1.4V

HCSL(高速電流轉(zhuǎn)向邏輯)0.0~0.75V

哪種石英晶體振蕩器輸出信號(hào)類型最適合您的應(yīng)用?讓我們看看它們的優(yōu)缺點(diǎn),我們將從基本開始,首先看一下單端選項(xiàng):

正弦波和削波正弦波:

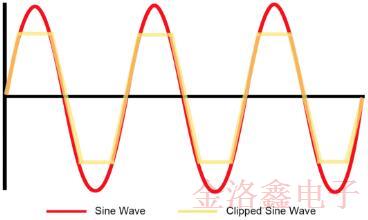

正弦波-是晶體或振蕩器電路的標(biāo)準(zhǔn)或”自然”信號(hào)輸出.它由一個(gè)基本正弦頻率輸出組成.線性正弦波輸出可在所有輸出中提供最佳的相位噪聲性能.這些非常適合需要高質(zhì)量輸出信號(hào)的應(yīng)用.削波正弦波-正弦波輸出受到控制,因此不會(huì)達(dá)到其最大高電平或低電平.這樣,您將創(chuàng)建一個(gè)方波輸出,而不會(huì)犧牲任何所需的相位噪聲性能.在此圖中,您可以看到紅色的正弦波和黃色的正弦波.

CMOS,HCMOS和LVCMOS:

CMOS,HCMOS和LVCMOS都屬于互補(bǔ)金屬氧化物半導(dǎo)體類別.它們是最適合低頻時(shí)鐘(通常低于250MHz)的方波數(shù)字輸出.這允許在時(shí)鐘輸出和芯片輸入之間直接連接.在大多數(shù)情況下,可以使用低值串聯(lián)電阻器來有效減少信號(hào)反饋并保持可靠的信號(hào)完整性.還有一些高速和低壓選項(xiàng)可能更適合您的特定需求.

TTL或晶體管到晶體管邏輯:

這是一個(gè)較舊的數(shù)字輸出標(biāo)準(zhǔn),并且已被CMOS技術(shù)取代.這是因?yàn)?/span>CMOS提供了有源晶振較低的成本和更好的噪聲性能.CMOS和TTL都非常適合低功耗,較高的輸出擺幅以及相對(duì)較低的成本.

差分輸出信號(hào)選項(xiàng):

差分輸出提供雙相異相180°的輸出信號(hào)線.這對(duì)信號(hào)質(zhì)量有很多好處,包括:

更好的上升和下降時(shí)間

出色的抖動(dòng)和相位噪聲性能

改進(jìn)的共模噪聲抑制

幫助減少電磁和射頻干擾

ECL或發(fā)射極耦合邏輯:

ECL主要是作為TTL的一種很好的替代方法引入的.ECL電路可以非常快速地改變狀態(tài),這使其更適合于高速數(shù)據(jù)傳輸.差分晶振輸出的缺點(diǎn)之一是它們需要明顯更高的電源電流才能工作.ECL在使用過程中還會(huì)使用負(fù)電源.嘗試連接到正極基礎(chǔ)電源設(shè)備時(shí),這可能會(huì)帶來挑戰(zhàn).

PECL和LVPECL:

PECL輸出經(jīng)常在高速時(shí)鐘分配電路中使用.這是因?yàn)?/span>PECL具有很高的抗噪能力,能夠在較長(zhǎng)的線路長(zhǎng)度上驅(qū)動(dòng)高數(shù)據(jù)速率,并且由于電壓擺幅較大而具有良好的抖動(dòng)性能.但是,PECL需要高功耗才能運(yùn)行,這是主要缺點(diǎn).LVPECL為千兆位以太網(wǎng)和光纖通道的使用奠定了良好的基礎(chǔ).LVPECL就像LVDS在電氣上一樣,但是提供更大的差分電壓擺幅和稍低的電源效率.LVPECL的輸出可能會(huì)帶來挑戰(zhàn),因?yàn)樾枰私觼戆l(fā)射電壓.同樣,芯片中的差分電路可能具有不同的輸入容差.確保檢查是否正確端接以達(dá)到最佳性能.

電流模式邏輯(CML):

CML具有與LVPECL相似的性能.這里的主要區(qū)別是CML不需要外部偏置.當(dāng)需要考慮低功耗時(shí),這使得CML可以替代LVPECL.

低壓差分信號(hào)(LVDS):

LVDS類似于LVPECL輸出,但是LVDS的功耗較低,并且電壓擺幅較小.LVDS通常用于滿足時(shí)鐘分配或背板收發(fā)器等高速數(shù)據(jù)傳輸需求.對(duì)于更高的數(shù)據(jù)速率,通常首選HCSL,CML或LVPECL,但比LVDS功耗更高.其他好處包括降低了對(duì)噪聲的敏感性,并且易于在CMOSIC中實(shí)現(xiàn).LVDS石英晶體振蕩器的缺點(diǎn)是與PECL相比,其抖動(dòng)性能降低,但是人們正在尋找新的技術(shù)來達(dá)到與LVPECL相同的抖動(dòng)性能.

高速電流轉(zhuǎn)向邏輯(HCSL):

HCSL具有較新的輸出標(biāo)準(zhǔn),例如LVPECL.HCSL的優(yōu)點(diǎn)之一是其高阻抗輸出和快速切換時(shí)間.建議使用10至30Ω的串聯(lián)電阻,以減少可能的過沖和振鈴.其他優(yōu)勢(shì)包括最快的開關(guān)速度,低功耗(介于LVDS和LVPECL之間)以及平均到良好的相位噪聲性能.

快速回顧:

為了易于使用:LVDS輸出在接收器處只需要一個(gè)電阻,而LVPECL在發(fā)送器和接收器上都需要端接.對(duì)于更高的頻率:LVDS,LVPECL和HCSL比CMOS具有更快的轉(zhuǎn)換速度,但需要更多的功率.為了獲得最低的功耗:如果您的頻率高于150MHz,我們建議使用CMOS或LVDS.為獲得最佳抖動(dòng)性能:如果頻率足夠低,請(qǐng)選擇LVPECL,LVDS和CMOS.

通過以上內(nèi)容相信大家對(duì)有源晶振的輸出邏輯都有了一定了解,如果還有不明白或者想知道更多的資料,歡迎大家在金洛鑫電子官網(wǎng)http://www.upap-pt.com/歡迎探討,我司做為專業(yè)的晶振廠家,非常樂意為大家解答疑惑.

ECS提供超全的振蕩器輸出類型指南

“推薦閱讀”

【責(zé)任編輯】:金洛鑫版權(quán)所有:http://www.upap-pt.com轉(zhuǎn)載請(qǐng)注明出處

相關(guān)技術(shù)支持

- FCD-Tech石英晶體F2520A-30-50-K-30-F-34.000MHz術(shù)語和定義理論

- ECS許多應(yīng)用需要石英振蕩器ECS-100AX-110.5和其他定時(shí)解決方案

- Abracon超小型ABS05-32.768KHZ-T音叉晶體專為節(jié)能MCU而優(yōu)化

- Bliley壓控晶振BVCS5-24.000MHZMDN-ABCBT如何工作?

- Microchip用于嵌入式系統(tǒng)的新型PIC18F06Q20微控制器(MCU)

- Golledge下一代GSRFTA0942A頻率控制5G網(wǎng)絡(luò)的解決方案

- CTS最新推出的OCXO完美應(yīng)用于各個(gè)領(lǐng)域

- 遙遙領(lǐng)先的Harmony Electronics Corp.用水晶增強(qiáng)安全駕駛

- 了解遙遙領(lǐng)先的SIWARD希華晶體振蕩器

- 領(lǐng)先全球Skyworks晶振為下一代Wi-Fi 6/6E設(shè)備提供前所未有的能效

手機(jī)版

手機(jī)版