差分振蕩器驅動自偏置差分輸入

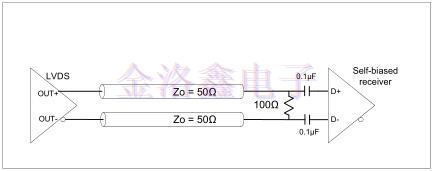

可輸出差分信號的差分晶振是近年來比較熱門的頻率元件之一,LVDS和LVPECL這兩種輸出模式,可降低產品周圍噪聲,和減低相位抖動,實現(xiàn)低功耗.許多差分接收器具有片上DC偏置電路和/或終端網絡.在這種情況下,振蕩器輸出應為交流耦合.如果需要外部偏置,則應根據(jù)接收器設備的數(shù)據(jù)表進行設計.LVDS或LVPECL振蕩器可用于驅動自偏置差分輸入.LVDS輸出需要更少的無源元件和更低的運行功率.如果700mV的LVDS擺幅足以用于接收器,則最好使用LVDS石英晶體振蕩器.圖18顯示了LVDS振蕩器與自偏置差分接收器的接口.

圖18:LVDS驅動器與具有內部端接和偏置的自偏置差分接收器的連接

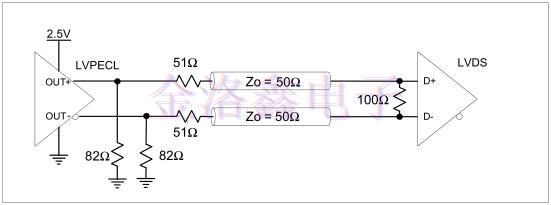

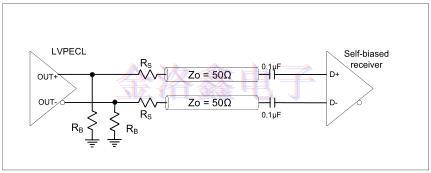

LVPECL輸出可在接收器處產生高達1.6V的差分擺幅.圖19示出了用于將LVPECL差分輸出晶振連接到自偏置差分接收器的示意圖.電阻RS在負載側產生一個帶終端的分壓器.可以通過選擇RS值來設置接收器輸入上的電壓擺動.RB為LVPECL驅動器提供直流偏置電流,其值可以從公式1計算得出.請注意,接收器將看到RS+50Ω的有效終端電阻值.

圖19:LVPECL驅動器與具有內部端接和偏置的自偏置差分接收器的連接

為了保持信號完整性,RS和RB應放置在傳輸線之前,盡可能靠近晶振.負載側終端網絡應盡可能靠近接收器輸入.

使用LVPECL驅動器驅動LVDS接收器

LVDS接收器可以用LVPECL時鐘信號驅動.這需要使用終端技術,將接收器側的信號置于LVDS信令要求之內.信號共模電壓和信號幅度是必須滿足的主要規(guī)格.為滿足LVDS規(guī)范,LVPECL信號幅度必須從1.6V降至0.75V.LVPECL驅動器的共模電壓取決于電源電壓,對于2.5V VDD,它與LVDS共模電壓相匹配.終端允許為具有2.5VLVPECL驅動器的LVDS接收器提供時鐘,如圖20所示.

圖20:將LVPECL驅動器與2.5V VDD連接到LVDS接收器

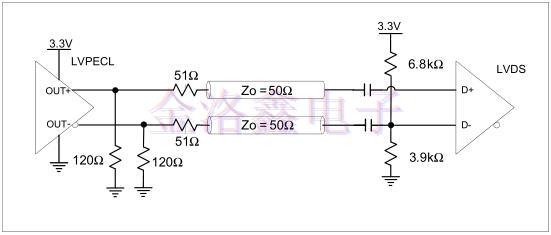

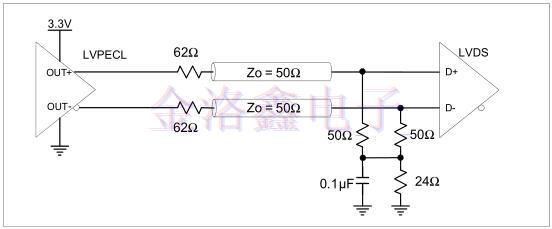

在3.3V VDD的情況下,LVPECL驅動器和LVDS接收器的共模電壓是不同的.圖21建議使用串聯(lián)電阻和Y端接來連接LVPECL驅動器和LVDS接收器.

圖21:將LVPECL驅動器與3.3V VDD連接至LVDS接收器

如果接收器具有片內匹配,則建議使用交流耦合,如圖22所示.共模由電阻分壓器設置.由于差分石英晶振等效電阻太高而不會導致正輸入和負輸入之間的不平衡,因此只有一個輸入有偏差.

圖22:將LVPECL驅動器與3.3V VDD連接到具有內部端接的LVDS接收器

手機版

手機版