差分振蕩器傳統(tǒng)HCSL和低功耗HCSL之間的終端區(qū)別是什么?

差分振蕩器傳統(tǒng)HCSL和低功耗HCSL之間的終端區(qū)別是什么?

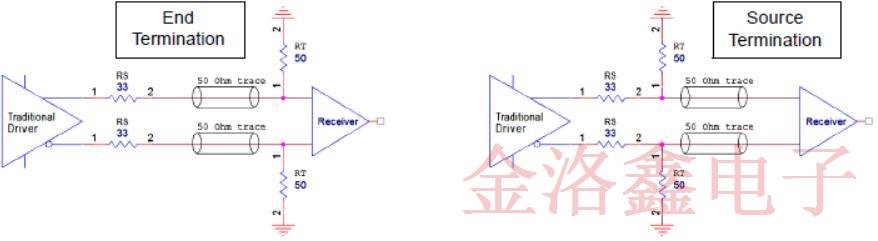

傳統(tǒng)的差分晶振HCSL端接使用50Ω電阻在PCB走線末端接地.后來,引入了另一種方法,將50Ω接地放置在驅(qū)動(dòng)器附近.這稱為源端接,它允許時(shí)鐘通過連接器,該連接器在電路處于活動(dòng)狀態(tài)(熱插拔)時(shí)可以拔出.LP-HCSL按照定義在驅(qū)動(dòng)程序端具有終結(jié)點(diǎn),并且可以與終結(jié)點(diǎn)終結(jié)點(diǎn)一起使用.此設(shè)置稱為雙端接.源端接與端接對(duì)接收器沒有影響.需要串聯(lián)電阻RS以避免過多的振鈴.

傳統(tǒng)HCSL終止

LP-HCSL終止

現(xiàn)在,在驅(qū)動(dòng)器附近,端接電阻(RS)與時(shí)鐘線串聯(lián).驅(qū)動(dòng)器本身設(shè)計(jì)為具有17Ω輸出阻抗,因此需要另外33Ω才能匹配50ΩPCB走線.右側(cè)的原理圖帶有端接電阻集成,因此不需要外部組件來驅(qū)動(dòng)50ΩPCB走線.

傳統(tǒng)的HCSL并不將驅(qū)動(dòng)程序本身用作終止的一部分.除了50Ω終端電阻之外,傳統(tǒng)的HCSL需要一個(gè)額外的33Ω串聯(lián)電阻,以避免驅(qū)動(dòng)器和50Ω端接走線之間的反射和振鈴.P-HCSL概念在同一33Ω串聯(lián)電阻中結(jié)合了避免主端接和振鈴的功能,從而減少了低電壓差分晶振數(shù)量計(jì)數(shù).某些應(yīng)用使用85Ω差分走線(或42.5Ω單端).對(duì)于這些應(yīng)用,我們建議RS=27Ω.IDT它還提供集成了用于85Ω系統(tǒng)的27ΩRS的時(shí)鐘.

雙重終止:某些接收器可能有芯片中的差分終端電阻.這些接收器是通常更通用,可以處理各種幅度和共模電壓,并且可能需要交流耦合時(shí)鐘信號(hào).LP-HCSL驅(qū)動(dòng)器可以輕松驅(qū)動(dòng)雙端接.在源極和源極都有終端電阻接收器將每個(gè)引腳的幅度降低至約400mVpp(差分為800mVpp).通常這種類型不是問題接收機(jī)以較小的幅度工作.400mVpp(800mVpp差分)電平甚至超過了150mVpp(300mVppPCIe參考時(shí)鐘的差分輸出振蕩器)輸入擺幅規(guī)范.

差分振蕩器傳統(tǒng)HCSL和低功耗HCSL之間的終端區(qū)別是什么?

“推薦閱讀”

【責(zé)任編輯】:金洛鑫版權(quán)所有:http://www.upap-pt.com轉(zhuǎn)載請(qǐng)注明出處

相關(guān)常見問題

- Cardinal卡迪納爾CX532Z-A5B3C5-70-12.0D18晶振常見問題

- 科普6G通信設(shè)備晶振重要指標(biāo)之抖動(dòng)與相位噪音的基礎(chǔ)知識(shí)CSX-750FBC25000000T

- 如何通過振蕩頻率評(píng)估石英晶體單元和振蕩電路匹配性X1G0002310272

- 溫度變化對(duì)石英晶體的影響CM200C32768EZFT

- 從組裝到最終產(chǎn)品——石英制造過程的最后階段1C241600CDAA

- 石英生產(chǎn)過程:從石英塊到石英坯CX2520DB16000D0GEJCC

- 生產(chǎn)振蕩石英晶體用的是真的巖石晶體嗎Q-SC32S0321060AAAF

- 石英晶振采購需要特別留心的幾個(gè)問題和技巧,致廣大用戶

- 如何看待低頻振蕩器的輸出電平與回波損耗

- 你知道什么時(shí)候使用MEMS晶振比較好以及它的價(jià)值嗎?

手機(jī)版

手機(jī)版